- 您现在的位置:买卖IC网 > Sheet目录369 > X28HC256SIZ-90 (Intersil)IC EEPROM 256KBIT 90NS 28SOIC

�� �

�

�

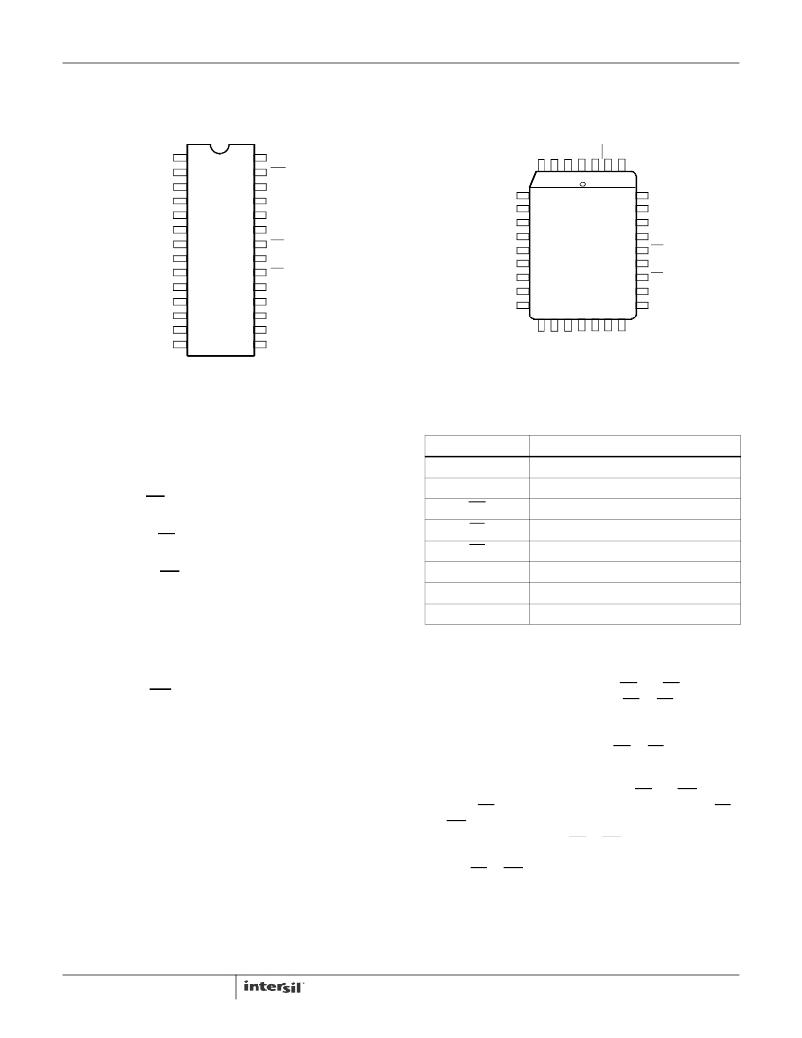

�X28HC256�

�Pinouts�

�X28HC256�

�(28� LD� FLATPACK,� PDIP,� SOIC)�

�TOP� VIEW�

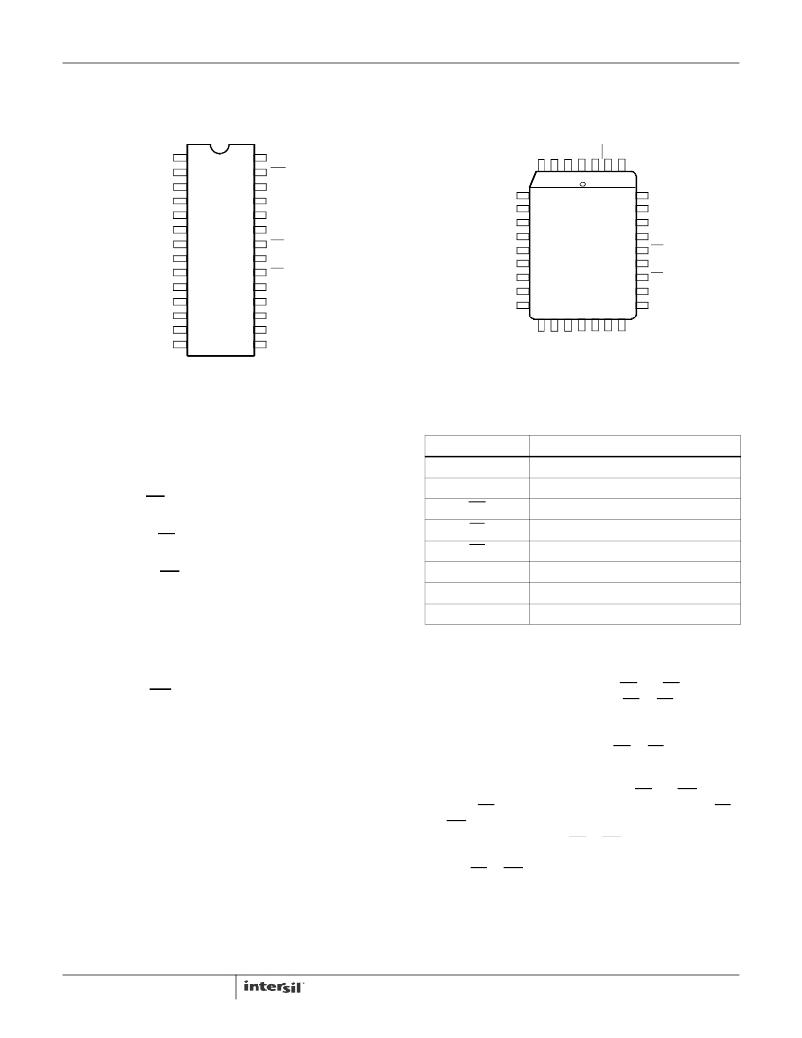

�X28HC256�

�(32� LD� PLCC,� LCC)�

�TOP� VIEW�

�A� 14�

�1�

�28�

�V� CC�

�9�

�25�

�A� 12�

�A� 7�

�A� 6�

�A� 5�

�A� 4�

�A� 3�

�A� 2�

�A� 1�

�A� 0�

�I/O� 0�

�I/O� 1�

�I/O� 2�

�V� SS�

�2� 27�

�3� 26�

�4� 25�

�5� 24�

�6� 23�

�7� 22�

�X28HC256�

�8� 21�

�9� 20�

�10� 19�

�11� 18�

�12� 17�

�13�

�16�

�14�

�15�

�WE�

�A� 13�

�A� 8�

�A� 9�

�A� 11�

�OE�

�A� 10�

�CE�

�I/O� 7�

�I/O� 6�

�I/O� 5�

�I/O� 4�

�I/O� 3�

�A� 6�

�A� 5�

�A� 4�

�A� 3�

�A� 2�

�A� 1�

�A� 0�

�NC�

�I/O� 0�

�4� 3� 2� 1� 32� 31� 30�

�5� 29�

�6� 28�

�7� 27�

�8� 26�

�X28HC256�

�10� 24�

�11� 23�

�12� 22�

�13� 21�

�14 15 16 17 18 19 20�

�A� 8�

�A� 9�

�A� 11�

�NC�

�OE�

�A� 10�

�CE�

�I/O� 7�

�I/O� 6�

�Pin� Descriptions�

�Pin� Names�

�Addresses� (A� 0� to� A� 14� )�

�The� Address� inputs� select� an� 8-bit� memory� location� during� a�

�read� or� write� operation.�

�Chip� Enable� (CE)�

�The� Chip� Enable� input� must� be� LOW� to� enable� all� read/write�

�operations.� When� CE� is� HIGH,� power� consumption� is�

�reduced.�

�Output� Enable� (OE)�

�The� Output� Enable� input� controls� the� data� output� buffers,�

�and� is� used� to� initiate� read� operations.�

�SYMBOL�

�A� 0� to� A� 14�

�I/O� 0� to� I/O� 7�

�WE�

�CE�

�OE�

�V� CC�

�V� SS�

�NC�

�DESCRIPTION�

�Address� Inputs�

�Data� Input/Output�

�Write� Enable�

�Chip� Enable�

�Output� Enable�

�+5V�

�Ground�

�No� Connect�

�Data� In/Data� Out� (I/O� 0� to� I/O� 7� )�

�Data� is� written� to� or� read� from� the� X28HC256� through� the� I/O�

�pins.�

�Write� Enable� (WE)�

�The� Write� Enable� input� controls� the� writing� of� data� to� the�

�X28HC256.�

�3�

�Device� Operation�

�Read�

�Read� operations� are� initiated� by� both� O� E� and� CE� LOW.� The�

�read� operation� is� terminated� by� either� CE� or� OE� returning�

�HIGH.� This� two� line� control� architecture� eliminates� bus�

�contention� in� a� system� environment.� The� data� bus� will� be� in�

�a� high� impedance� state� when� either� OE� or� CE� is� HIGH.�

�Write�

�Write� operations� are� initiated� when� both� CE� and� WE� are�

�LOW� and� OE� is� HIGH.� The� X28HC256� supports� both� a� CE�

�and� WE� controlled� write� cycle.� That� is,� the� address� is� latched�

�by� the� falling� edge� of� either� CE� or� WE,� whichever� occurs�

�last.� Similarly,� the� data� is� latched� internally� by� the� rising� edge�

�of� either� CE� or� WE,� whichever� occurs� first.� A� byte� write�

�operation,� once� initiated,� will� automatically� continue� to�

�completion,� typically� within� 3ms.�

�FN8108.3�

�September� 21,� 2011�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

X28HC64JIZ-90

IC EEPROM 64KBIT 90NS 32PLCC

XCARD XK-1A

DEV KIT EVENT-DRIVEN PROC XS1-L1

XCARD XTAG-2

ADAPTER USB DEBUGGER JTAG XSYS2

XE8000EV101

EVAL BOARD FOR XE8801AMI027LF

XG4E-6431-S012

CONN PLUG 64POS 1A OPENED COVER

XLNRC

RAPID OUTPUT CONNECTOR

XLT80PT3

SOCKET TRAN ICE 80MQFP/TQFP

XRP6658EVB

EVAL BOARD FOR XRP6658

相关代理商/技术参数

X28HC256SM-12

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:5 Volt, Byte Alterable EEPROM

X28HC256SM-12,

制造商:ROCHESTER 制造商全称:ROCHESTER 功能描述:LOW POWER CMOS EEPROM with hi-speed page write capability 256K EEPROM

X28HC256SM-15

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:5 Volt, Byte Alterable EEPROM

X28HC256SM-70

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:5 Volt, Byte Alterable EEPROM

X28HC256SM-90

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:5 Volt, Byte Alterable EEPROM

X28HC256SMB-12

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:5 Volt, Byte Alterable EEPROM

X28HC256SMB-15

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:5 Volt, Byte Alterable EEPROM

X28HC256SMB-70

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:5 Volt, Byte Alterable EEPROM